Allegro X

Next-Gen Integrated PCB & System Engineering

Allegro X Tackles Emerging Industry Challenges

Allegro X from Cadence is the industry’s first electronics design platform that integrates logic/physical design, system analysis, and design data management for PCB and system design.

From concept to manufacturing, Allegro X unifies and upgrades the best-in-class Allegro portfolio of tools with performance enhancements, new automations, and system integrations, leading to:

- Increased overall productivity

- Reduced development costs

- More innovative products

- Multifaceted competitive advantage

What is Allegro X?

Integrated Tools on One Platform

- Allegro PCB Designer

- System Capture Schematic

- Reliability

- Allegro X AI

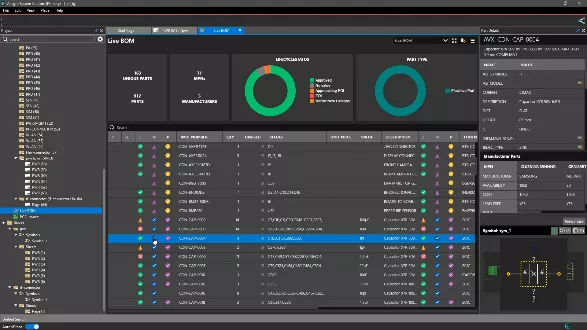

- LiveBOM

- EE Cockpit

- 3D Engine

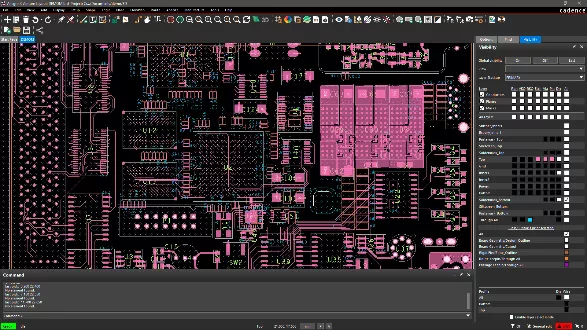

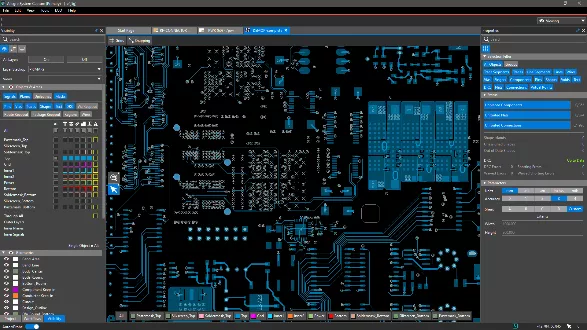

Classic Allegro PCB Design

- Advanced routing capabilities for complex and high-speed PCB designs

- Constraint- and rules-driven methodology

- Made for design replication & reuse

- Powerful performance enhancements

- Allegro X AI placement and route engine

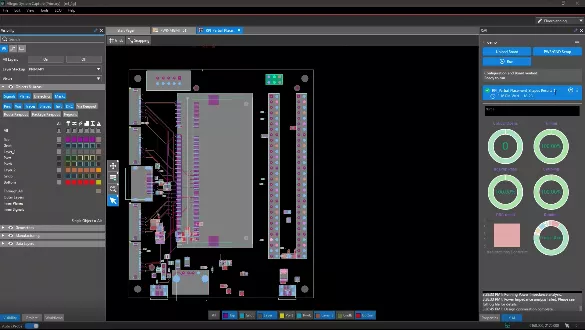

AI-Enabled

- Automated placement and routing

- Better designs, made much faster by AI

- Easy to validate on-platform

- On-cloud compute

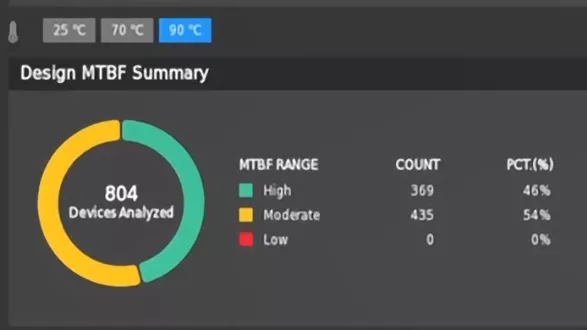

Design Reliability

- Reliability analysis of individual components at the schematic level

- Driven from component datasheets

- Sophisticated electrical stress calculation & reporting

- MTBF analysis

- Over 30 advanced auditing checks

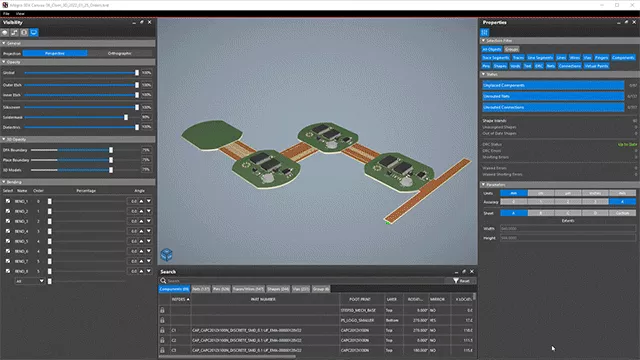

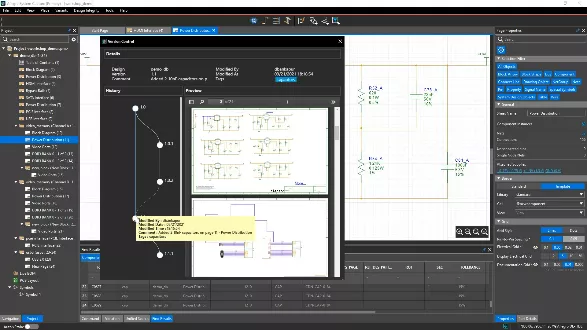

electrical Engineer's Cockpit

- Unified environment for the EE’s needs

- Common interface between system capture and layout

- Made for concurrent design

- PCB visualization at any time

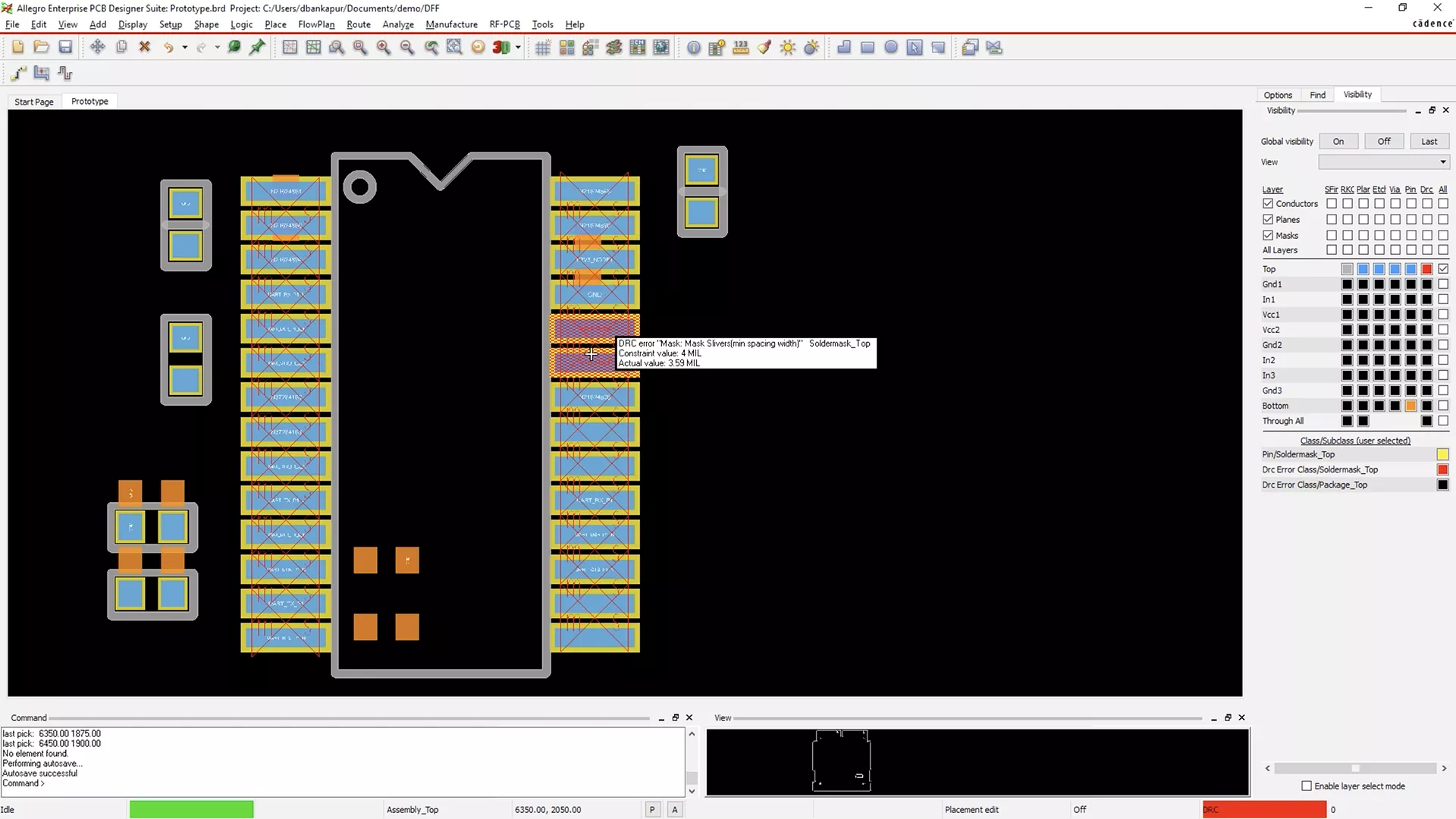

Design For Manufacturing

- The DesignTrue DFM tool provides realtime, in-design manufacturability validation

- Reduce rework and shorten design cycles

- Import DFM rules from certified manufacturers directly into Allegro X

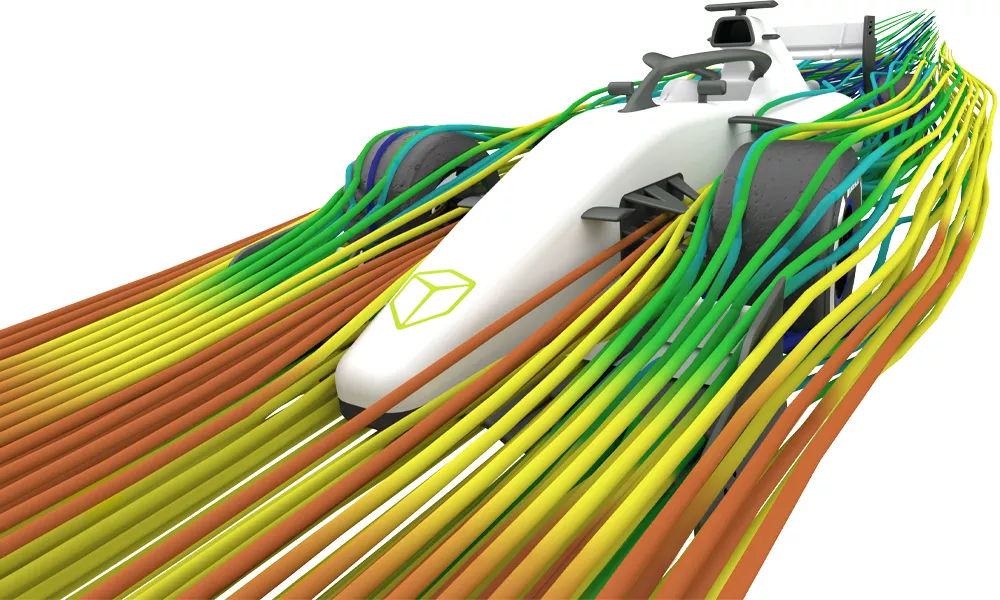

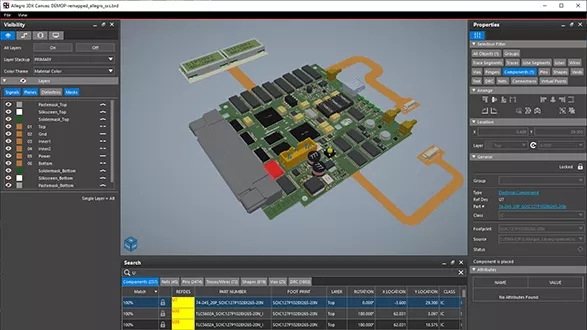

MCAD/ECAD Collaboration

- Mechanical-conscious system capture

- Multiphysics analysis

- Enhanced high-performance 3D viewer and CAD export

- PDM connectivity to MCAD data

- See the SOLIDWORKS connection in our MCADX demo >>

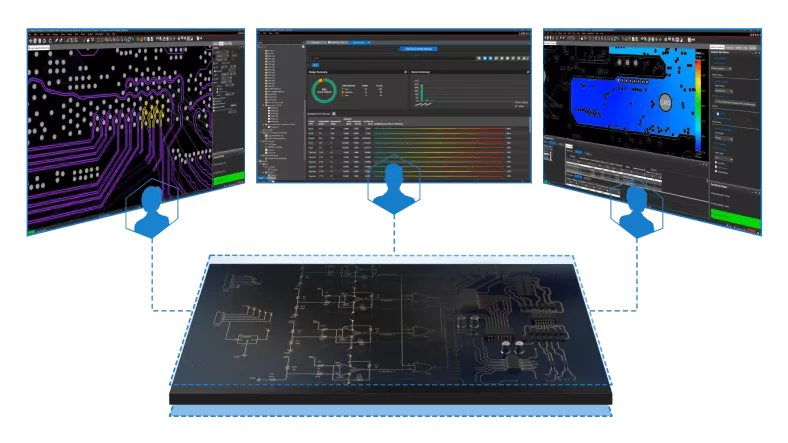

Concurrent Design with Pulse

- Unified library authoring

- JedAI data & analytics integration

- 3DEXPERIENCE and other PLM integration

- Dassault Systèmes MBSE integration

High Performance

- Enhanced GPU engine

- 2D rendering up to 50x faster

- 3D rendering up to 40x faster

- Supports 10M+ data objects

Compare Allegro X Packages

AWR Interface

Multi-Style Design Creation (Tabular/Graphical/Language)

Allegro Design Entry (System Capture)

System Level Design (3 Boards)

System Level Design (Unlimited Boards)

Enable Access to Centralized Pulse

Audit Rules in Design Integrity

Variants Flow

MTBF Analysis

PCB Editor

Intelligent Topology Apply of Electrical Constraint Rule Set (ECSets)

PCB Interconnect Bundle, Flow Creation, Editing and Controls

Rigid Flex Design

PCB Design for Assembly, DFA Placement Matrix Rules

PCB Editor Floorprint Editor

Auto-interactive Breakout Technology

Auto Connect - Direct-to-Etch Auto Routing for Selected Clines

Dynamic Flow Creation

Auto-interactive Trunk Routing

Plan Spatial Feasibility Analysis and Feedback

Generate Topological Plan

Convert Topological Plan to Traces (CLINES)

Allegro RF PCB Aware Technology

MCAD/ECAD Incremental Design Data Exchange (EDMD)

New 3D Canvas

Embedded Packaged Components

Dynamic Fillet Glossing Option

AWR Microwave Office Interface

Layer Base Dynamic Shape Control

Vision (Routing, Placement)

Automatic Power Plane Generation 23.1

Dynamic Backdrilling

Allegro Router (High Performance Level)

Design for Manufacturing

Advanced Rules

Allegro PCB Router 256U

Allegro PCB Router 6U

High Speed Paramterized Structures

Intelligent, Navigatable PDF Output from PCB Editor

RouteVision

HDI Micro-via Stack Editing

Auto-interactive Delay Tuning (AiDT)

Auto-interactive Phase Tuning (AiPT)

TimingVision

DesignTrue DFM Rule Aggregator

DesignTrue DFM: In-design DFM, DFA: core Checks (100+ Checks)

DesignTrue DFM: In-design DFM, DFA: Flex Checks

DesignTrue DFM: In-design DFM: DFF, DFA and DFT Advance Checks (1000+ Checks)

Table Driven Constraints (Physical, Spacing, Electrical)

Special Routing (Tabbed, Weave, offset, Snake, Scribble, Coutour)

Generic GPU Acceleration

Electrical Rules (Reflection, Timing, Crosstalk)

Electrical Routing Rules: Impedances and Delay

Region-based Rules

Diff Pairs, Physical, Spacing, Properties, SameNet Rules Worksheet

RAVEL Checker

RAVEL Developer

Estimated Crosstalk Rules

Derived Constraint Rule Sets (Physical Spacing)

X:AI, JedAI, and Pulse Capable

LiveBOM

Backward Compatable to 17.2

Can access SamacSys and UltraLibrarian for parts

Additional Resources

Take Advantage of GoEngineer’s Extensive Knowledge Base and Resources

Find a Solution

Our robust Knowledge Base contains over 12,000 resources to help answer your product design questions. From basic CAD questions to in-depth guides and tutorials, find your solution here. Find a Solution

PROFESSIONAL TRAINING

Improve your skills with professional training and certifications in SOLIDWORKS, CAM, 3D Printing, and 3D Scanning offered four ways: self-paced, online, on-site, or in-classroom. Certified Training Courses

BLOG

#1 Technical Resource Worldwide - Right at your fingertips. Search or browse through hundreds of SOLIDWORKS tips & tricks, additive manufacturing product developments, announcements, how-to guides, and tutorials. Blog

YouTube Channel

Our YouTube channel hosts hundreds of educational tutorials, product demonstrations, recorded webinars, and best practices for all of our products and services. GoEngineer's YouTube Channel

ONLINE STORE

Order 3D printing materials and consumables, enroll in SOLIDWORKS training classes, and buy official GoEngineer gear directly from our online store. Online Store

WEBINARS

Our engineering webinars are hosted by some of the top experts in the industry. They are always recorded, always free, and always offer a live Q&A. WEBINARS

3D Printing Services

Need to 3D print a part? Our Additive Manufacturing experts will 3D print your part and deliver it to you using the latest technology on one of our professional FDM, PolyJet and SL 3D printers. 3D Printing Services